215 Test3

215 : Test3

- Author: Shaos

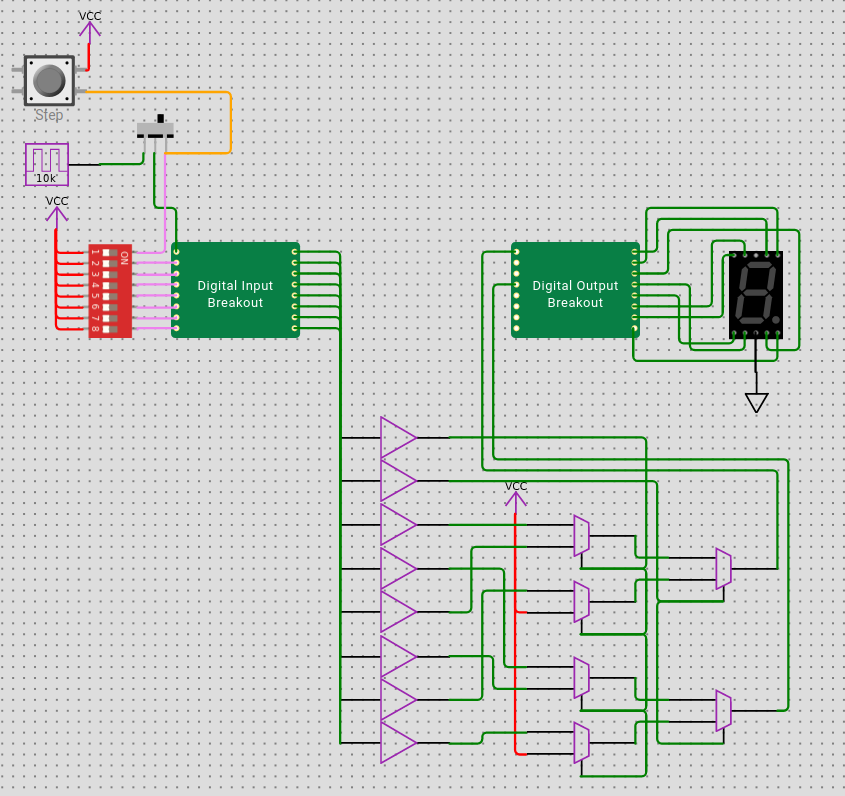

- Description: Binary Coded Ternary Test

- GitHub repository

- Clock: 0 Hz

How it works

Should work as ternary selector

How to test

Set inputs, read outputs

IO

| # | Input | Output |

|---|---|---|

| 0 | C+ | segment a |

| 1 | C- | segment b |

| 2 | N+ | segment c |

| 3 | N- | segment d |

| 4 | O+ | segment e |

| 5 | O- | segment f |

| 6 | P+ | segment g |

| 7 | P- | dot |